# Processor Hardware and Instruction Set Architecture

by: Tassadaq Hussain

Director Centre for Al and BigData

Professor Department of Electrical Engineering

Namal University Mianwali

### **Collaborations:**

Barcelona Supercomputing Center, Spain

European Network on High Performance and Embedded Architecture and Compilation

Pakistan Supercomputing Center

# **Topics**

### 1. Basic Processor Architecture

- 2. Different Types of Processor Architectures

- 3. RISC-V Processor Architecture

- 4. RISC-V Instruction Set Architecture

- 5. Programming RISC-V using assembly language

### **Basic Processor Architecture**

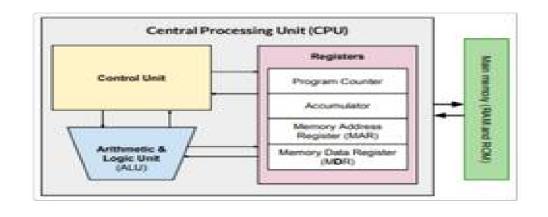

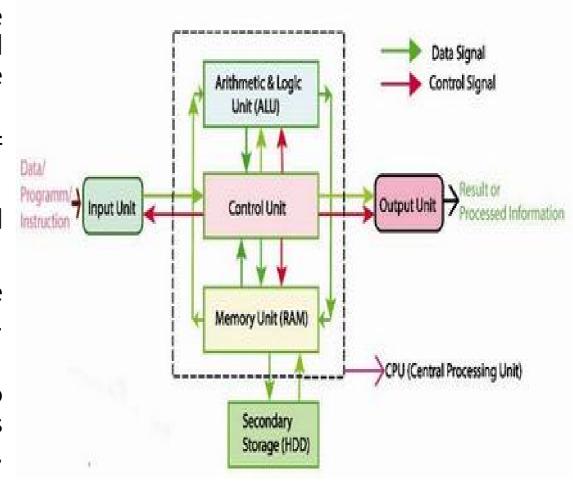

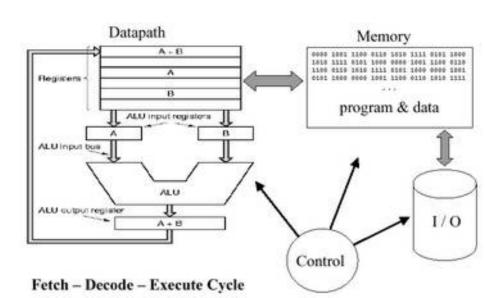

Processor Architecture refers to the design and organization of a processor's central processing unit (CPU).

### **Components of Processor:**

- Arithmetic and Logic Unit: Performs mathematical calculations.

- Control Unit: Control the overall processing of the processor.

- Decoders Unit: Convert coded instructions into signals that can control other components.

- Registers: Hold data, instructions, and addresses temporarily during processing.

- **Buses:** Electrical pathways that transmit data and signals between components. Types include the data bus, address bus, and control bus.

- Clock: Generates timing signals to synchronize the operations of the CPU components. The clock speed determines how many instructions per second the CPU can execute.

- **Instruction Set Architecture (ISA)**: Defines the set of instructions the CPU can execute

- Cache: Stores frequently accessed data and instructions to speed up processing.

- Memory Management Unit (MMU): Handles the translation of virtual addresses to physical addresses. Manages memory protection and caching.

- Input/Output (I/O) Interfaces: Allow the CPU to communicate with peripheral devices. Include ports and controllers for devices such as keyboards, mice, and storage.

- Power Control Unit:

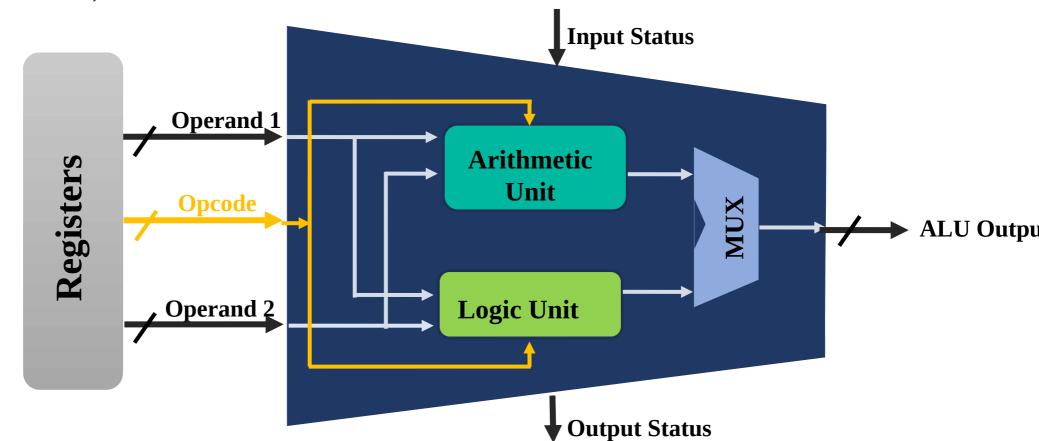

### **Arithmetic Logic Unit ALU:**

In computing, an arithmetic logic unit (ALU) is a combinational digital circuit that performs arithmetic and bitwise operations on integer binary numbers.

It is a fundamental building block of many types of computing circuits, including the central processing unit (CPU) of computers, FPUs, and graphics processing units (GPUs).

#### **Functions of ALU:**

| Basic Operations      | Basic Instructions                                                        |

|-----------------------|---------------------------------------------------------------------------|

| Arithmetic operations | Addition, Subtraction, Multiplication, division                           |

| Logical operations    | Logical Sum(OR), Logical Product(AND), Logical negation (NOT)             |

| Comparison            | Comparison Instruction (size compare)                                     |

| Branch                | Branch instructions to alter the instruction sequence based on conditions |

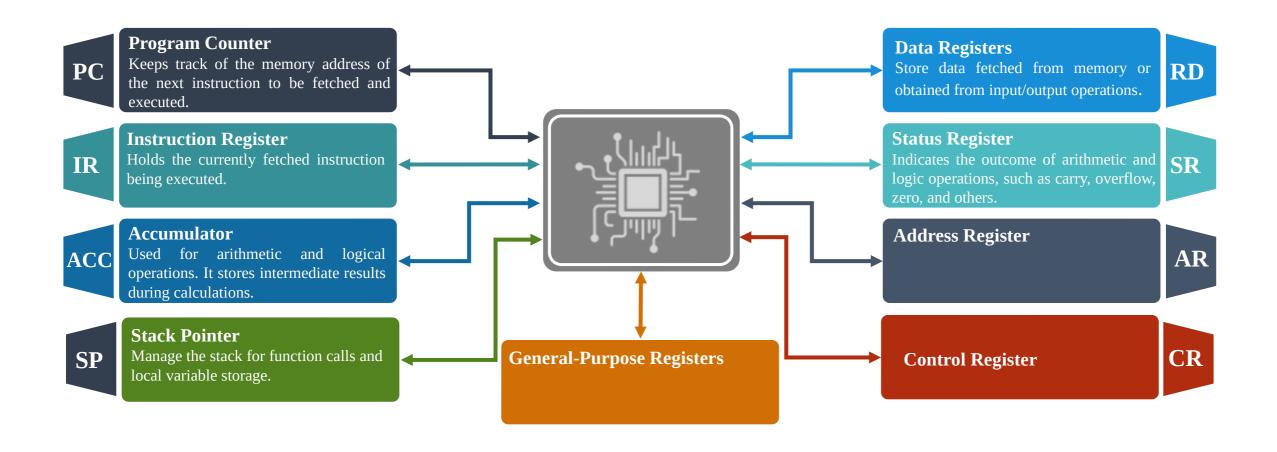

### **Registers**

- Registers are a type of computer memory built directly into the processor that is used to store and manipulate data during the execution of instructions.

- A register may hold an instruction, a storage address, or any kind of data (such as a bit sequence or individual characters).

# Registers in Processor Architecture

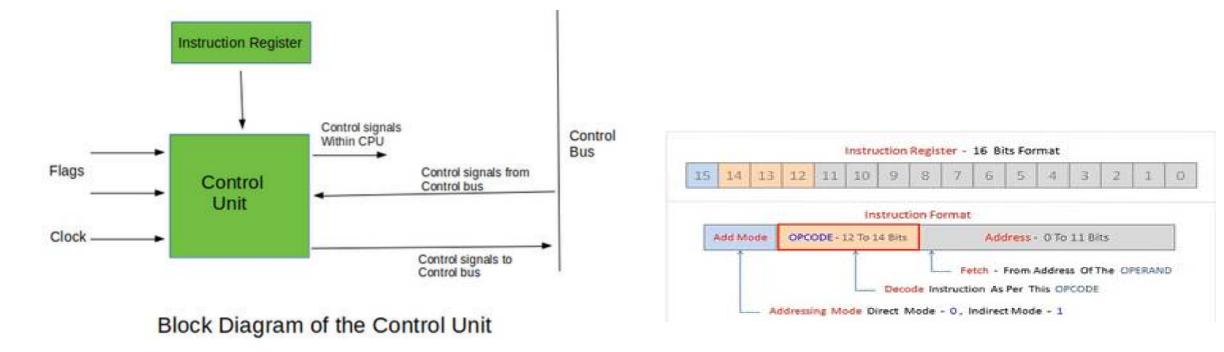

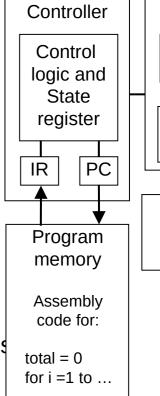

### **Control Unit:**

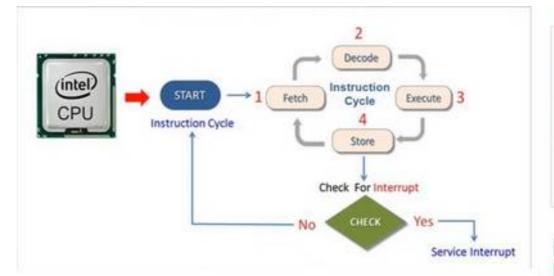

The control unit controls all the operations of the processor. It retrieves, decodes and executes the code instructions one-by-one in the order they are stored in the main memory.

It instructs the arithmetic logic unit, memory, input/output devices how to respond to the instructions of the program.

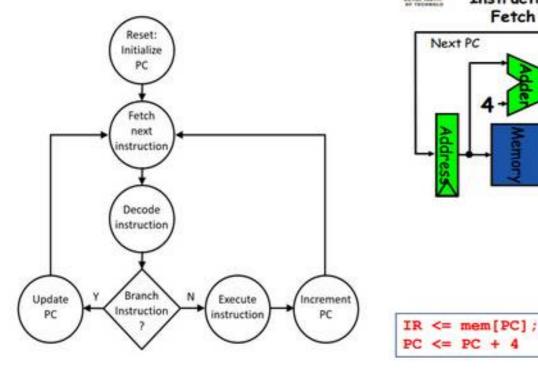

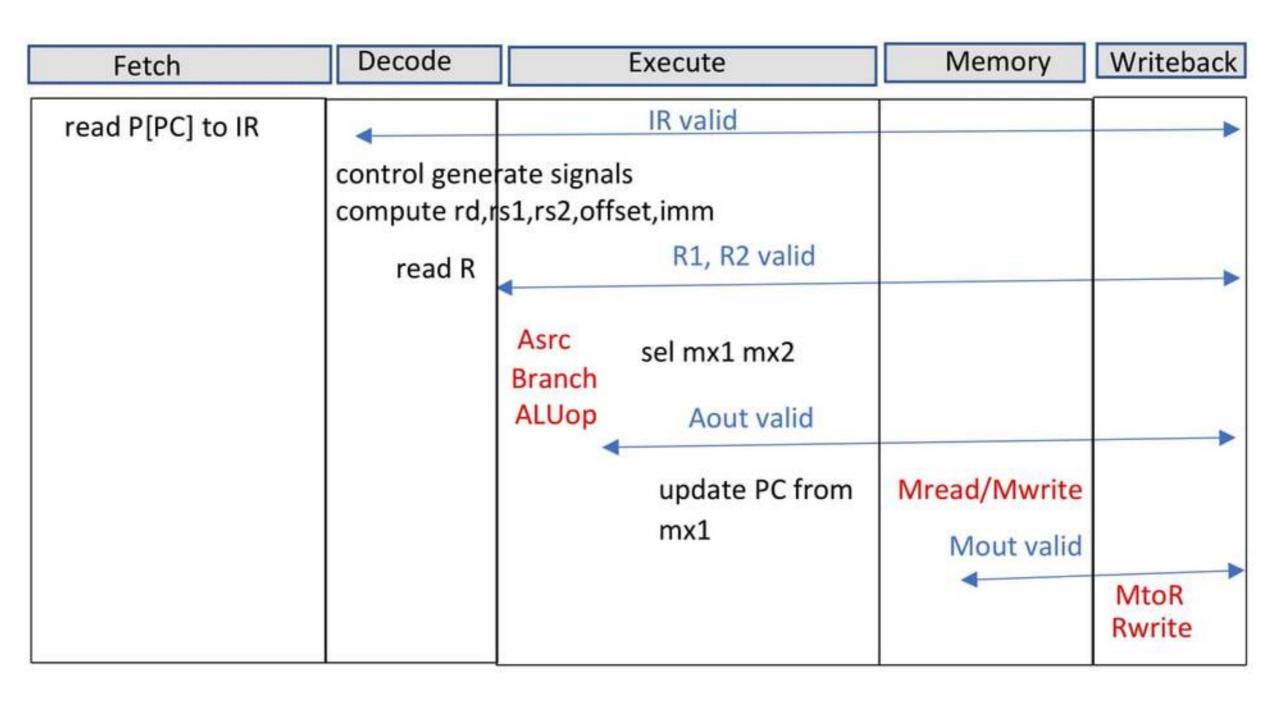

# Stages: Execution Clock Cycles

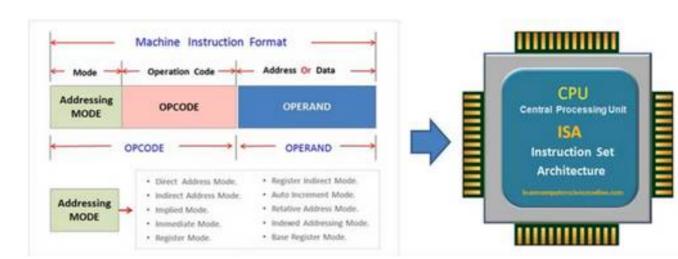

### Instruction Set Architecture (ISA)

An **Instruction Set Architecture (ISA)** is part of the abstract model of a computer that defines how the CPU is controlled by the software.

- The ISA acts as an interface between the hardware and the software, specifying both what the processor is capable of doing as well as how it gets done.

- The ISA defines the supported data types, the registers, how the hardware manages main memory, key features (such as virtual memory), which instructions a microprocessor can execute, and the input/output model of multiple ISA implementations.

- Provides:

- **Programmability**

- **Flexibility**

- **Reusablility**

- **Adaptability**

- **Accessibility**

Machine Instructions

11010100001100101

0111010101101101

1101011101100111

0101110101101100

111101010101010011

0101011101101101

# Instruction Set Format

| 1 27    | 26   | 25   | 24   | 20   | 19       | 15 | 14  | 12  | 11    | 7       | 6      | 0     |

|---------|------|------|------|------|----------|----|-----|-----|-------|---------|--------|-------|

| funct   | 7    |      | rs   | 2    | rs1      |    | fun | ct3 | r     | d       | opcode | R-ty  |

| in      | m[]  | 11:0 | ]    |      | rsl      |    | fun | ct3 | r     | d       | opcode | 1-typ |

| imm[1   | 1:5] |      | rs   | 2    | rsl      |    | fun | ct3 | imm   | [4:0]   | opcode | S-ty  |

| imm[12] | 10:5 | [    | TS   | 2    | rsl      |    | fun | ct3 | imm[4 | 4:1[11] | opcode | B-ty  |

|         |      |      | im   | m[31 | :12]     |    |     |     | r     | d       | opcode | U-ty  |

|         | - 3  | mn   | [20] | 10:1 | 11 19:13 | 2] |     |     | r     | d       | opcode | J-ty  |

A form of representation of an instruction composed of fields of binary numbers."

#### **Fields of instruction:**

There are several fields of the instruction that serve a specific role in the format. Some common are fields are given below:

#### 1. Opcode:

- Specifies the operation to be performed (e.g., add, subtract, load, store).

- Determines what action the CPU should take.

#### 2. Operand:

- The data or the addresses of the data on which the operation is to be performed.

- Can include immediate values, register addresses, or memory addresses.

#### 3. Addressing Modes:

Processor uses different Addressing modes Common modes include: immediate, direct, indirect, register, and indexed addressing.

#### 4. Registers:

Specifies which CPU registers are to be used in the operation.

Could include source and destination registers.

### **Instruction Types**

A computer's instructions can be any length and have any number of addresses.

- The arrangement of a computer's registers determines the different address fields in the instruction format.

- The instruction can be classified as three, two, and one address instruction or zero address instruction, depending on the number of address fields.

Based on these differences the instructions are classified as

- 1) Three Address Instruction

- 2) Two Address Instruction

- 3) One Address Instruction

- 4) Zero Address Instruction

# **Three Address Instruction:**

Three-address instruction is a format of machine instruction. It has one opcode and three address fields.

One address field is used for destination and two address fields for source.

| OPCODE | DESTINATION | SOURCE 1 | SOURCE 2 |

|--------|-------------|----------|----------|

|--------|-------------|----------|----------|

### **Example:**

| ADD | R1, A, B  | R1 = M[A] + M[B] |

|-----|-----------|------------------|

| ADD | R2, C, D  | R2 = M[C] + M[D] |

| MUL | X, R1, R2 | M[X] = R1 * R2   |

### Two Address Instruction:

Two-address instruction is a format of machine instruction. It has one opcode and two address fields which may be memory locations or registers..

One address field is used for destination and one address field for source.

For example, a two-address instruction might add the contents of two registers together and store the result in one of the registers.

| OPCODE I | DESTINATION | SOURCE |

|----------|-------------|--------|

|----------|-------------|--------|

### **Example**

:

| MOV | R1, A | R1 = M[A]      |

|-----|-------|----------------|

| ADD | R1, B | R1 = R1 + M[B] |

### **One Address Instruction:**

These instructions specify one operand or address, which typically refers to a memory location or register.

The instruction operates on the contents of that operand, and the result may be stored in the same or a different location.

For example, a one-address instruction might load the contents of a memory location into a register.

| OPCODE | DESTINATION |

|--------|-------------|

|--------|-------------|

**Example:**

| STORE | Т | M[T] = AC |

|-------|---|-----------|

| LOAD  | С | AC = M[C] |

### **Zero Address Instruction:**

These instructions do not specify any operands or addresses. Instead, they operate on data stored in registers or memory locations implicitly defined by the instruction.

For example, a zero-address instruction might simply add the contents of two registers together without specifying the register names.

# Types of Instructions and Addressing Modes

Implied Mode

Example: CLC; Clear the carry flag, no operands needed

**Immediate Mode**

Example: ADDI x1, x2, 10; Add immediate value 10 to register x2 and store result in x1

Register Mode

Example: MOV r0, r1; Move the contents of register r1 to register r0

Register Indirect Mode

Example: LW \$t0, 0(\$t1); Load the word at the address in \$t1 into \$t0

#### **Autodecrement Mode**

Example: MOV -(R1), R0; Decrement R1 and then move the value at the new address in R1 to R0

#### **Autoincrement Mode**

Example: MOV (R1)+, R0; Move the value at the address in R1 to R0, then increment R1

#### Direct Address Mode

Example: LDA \$4000; Load the accumulator with the value at memory address \$4000

#### **Indirect Address Mode**

Example: JMP (\$1234); Jump to the address stored at memory location \$1234

#### **Indexed Addressing Mode**

Example: MOV AX, [BX+SI]; Move the value at address (BX + SI) into AX

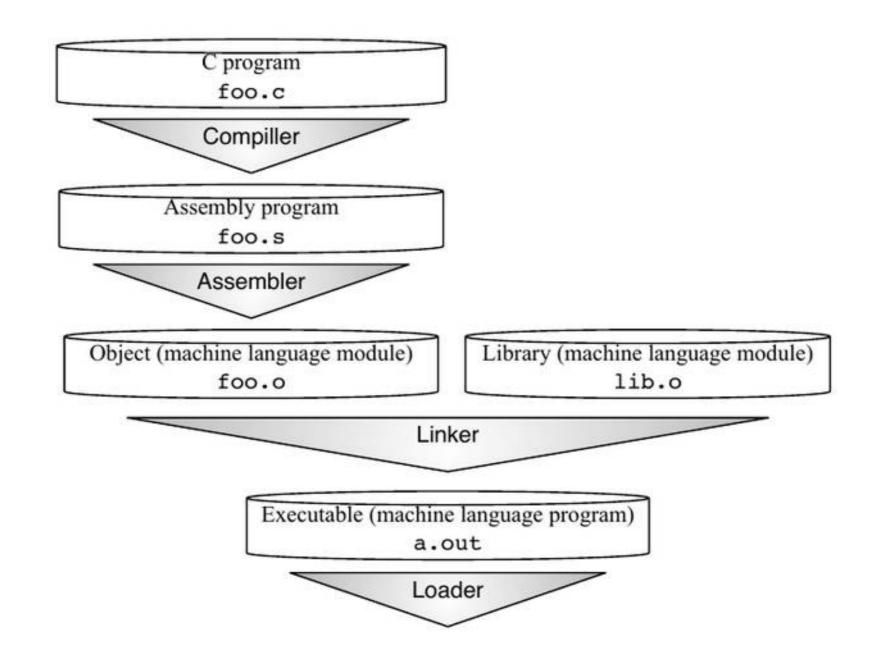

```

swap(size_t v[]. size_t k)

High-level

language

program

size_t temp:

(in C)

temp - v[k]:

v[k] = v[k+1]:

v[k+1] = temp:

Compiler

Assembly

swap:

slli x6. x11. 3

language

x6. x10. x6

add

program

I W

x5.0(x6)

(for RISC-V)

x7.4(x6)

Tw.

x7.0(x6)

SW

SW

x5.4(x6)

jalr x0. 0(x1)

Assembler

Binary machine

language

program

```

(for RISC-V)

00000000001101011001001100010011 00000000011001010000001100110011 00000000000000011001100101010000011 000000000111001100110000000100011 00000000010100110011010000100011 000000000000000001000000001100111

Tech

# Instructions Types

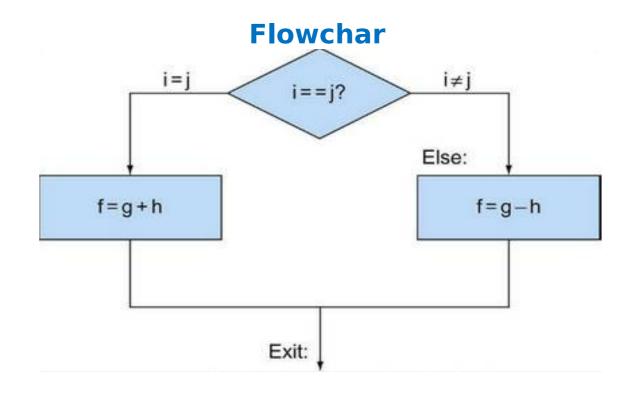

R-type: Integer computation instructions on registers.

I-type: Integer computation instructions on registers and immediate values. Also

includes JALR, Load instructions.

S-type: Store instructions.

B-type: Branch instructions.

U-type: Special instructions like LUI, AUIPC.

J-type: Jump instructions like JAL.

| 31      | 30        | 25 24  | 21     | 20    | 19  | 15 14    | 13  | 2 11 8   | 7      | 6      | 0   |        |

|---------|-----------|--------|--------|-------|-----|----------|-----|----------|--------|--------|-----|--------|

| fı      | met7      |        | rs2    |       | rs1 | func     | t3  | r        | d      | opc    | ode | R-typ  |

|         | imm       | [11:0] |        |       | rsl | func     | et3 | r        | d      | ope    | ode | I-type |

| imı     | m[11:5]   | T      | rs2    |       | rsl | func     | t3  | imn      | n[4:0] | ope    | ode | S-type |

| imm[12] | imm[10:5] |        | rs2    |       | rs1 | func     | et3 | imm[4:1] | imm[1  | 1] opc | ode | B-type |

|         |           | in     | nm[31: | 12]   |     |          |     | r        | d      | opc    | ode | U-type |

| imm[20] | imm       | [10:1] | i      | mm[11 | im  | m[19:12] |     | r        | d      | opc    | ode | J-type |

# Important Parameters of a Processor

#### ISA →

- Arithmetic Logic Unit (ALU): Performs arithmetic and logical operations.

- Floating Point Unit (FPU): Performs floating-point arithmetic operations (optional in some architectures).

- Registers: Small, fast storage locations within the CPU, used to store data and instructions temporarily.

- Control Unit (CU): Directs operations of the processor, including instruction decoding and execution control.

- Program Counter (PC): Holds the address of the next instruction to be executed.

- Instruction Register (IR): Holds the current instruction being executed.

- Branch Predictor: Predicts the outcome of conditional branches to reduce instruction execution delays.

- Bus Interface Unit (BIU): Manages data flow between the processor and external components like memory or peripherals.

- Pipeline: Allows overlapping execution of instructions to improve performance.

- Cache Memory: High-speed memory closer to the CPU, used to store frequently accessed data.

- Memory Management Unit (MMU): Manages memory access and translation between physical and virtual addresses.

- Input/Output (I/O) Unit: Handles communication with external devices.

### **Control Unit**

- The Control Unit (CU) of a processor is responsible for directing the flow of data and the sequence of operations within the CPU. It coordinates the activities of the processor by interpreting and executing instructions. The CU can be broken down into several sub-parts, each handling specific tasks. Here are the main sub-parts:

- Instruction Decoder

- Sequencing Logic

- Control Logic Circuit

- Control Signal Generator

- Program Counter (PC) Control

- Status Flag Register

- Microprogram Control Storage

- Timing and Clock Control

- Branch and Jump Control

- Interrupt Control

clock and reset

debug ports (only for testing)

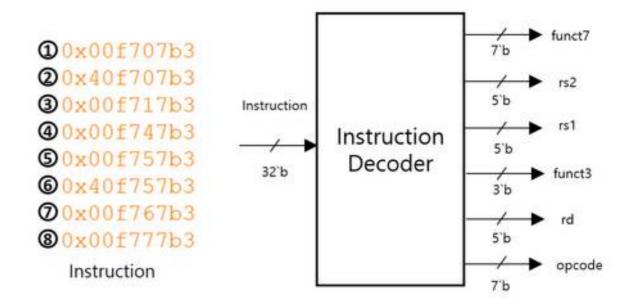

#### 1. Instruction Decoder:

Decodes the fetched instruction from memory into signals that specify the operation to be performed.

Breaks down machine code into control signals that tell various parts of the processor what to do next.

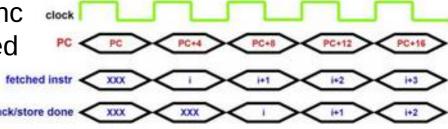

### 2. Sequencing Logic:

are carried out by determining the next instruction to be executed (through the Program Counter).

Manages the fetching, decoding, and execution cycle of instructions.

Synchronizes the processor's operation, often tied to the system clock.

Controls the order in which operations

| clock cycle | 1  | 2  | 3  | 4   | 5   |

|-------------|----|----|----|-----|-----|

| 1           | IF | ID | EX | МЕМ | WB  |

| 2           |    | IF | ID | EX  | МЕМ |

| 3           |    |    | IF | ID  | EX  |

| 4           |    |    |    | IF  | D   |

| 5           |    |    |    |     | IF  |

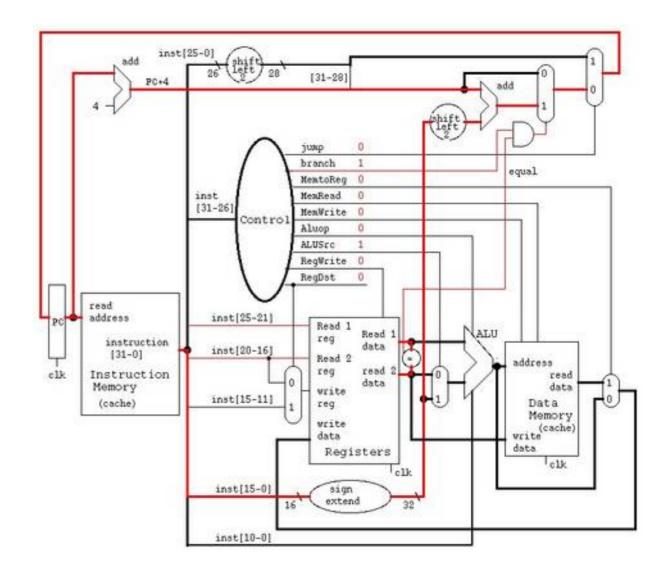

### • 3. Control Logic Circuit:

Contains the logic gates and combinational circuits that generate control signals based on the instruction decoded.

These control signals manage the internal data flow, timing, and operation of functional units (ALU, registers, etc.).

### 4. Control Signal Generator:

Generates the necessary control signals that dictate the actions of other parts of the CPU (ALU, memory interface, etc.).

These signals direct data movement, ALU operation, register writes, and memory accesses.

- ALU Control: ALUOp , ALUSrc

- Register Control: RegWrite, RegRead

- Memory Control: MemRead, MemWrite, MemToReg

- · Branch/Jump Control: Branch , Jump , PCSrc

- Immediate Generation Control: ImmSrc

- Instruction Fetch Control: PCWrite, IFIDWrite

- · Pipeline Control: Stall, Flush, ForwardA, ForwardB

- · CSR Control: CSRRead , CSRWrite

### • 5. Control Instruction (PC):

Manages the Program Counter, which holds the address of the next instruction to be executed. Handles instruction sequencing, updating the PC after each instruction or adjusting it for branch and jump operations.

### • 6. Status Flag Register:

Contains flags that hold status information about the result of previous operations (e.g., Zero, Carry, Overflow, Sign flags).

These flags help the Control Unit make decisions regarding branching and conditional operations.

### • 7. Timing and Clock Control:

Coordinates the timing of operations across the CPU with the help of clock signals.

Ensures that all parts of the processor operate in sync and that each step of the instruction cycle is executed at the correct time.

#### • 8. Branch and Jump Control:

Manages control transfer instructions, such as branches, jumps, and calls.

Works with the Branch Prediction Unit (in modern processors) to optimize branching and minimize delays caused by pipeline stalls.

#### • 9. Interrupt Control:

Handles interrupts by suspending the current execution and transferring control to the appropriate interrupt service routine.

Prioritizes interrupts and manages interrupt requests.

# • 10. Microprogram Control Storage (in microprogrammed Cus):

In microprogrammed control units, the control signals are generated by executing a sequence of microinstructions stored in a microprogram memory (control memory).

Each instruction in the CPU is mapped to a set of microinstructions that control specific low-level operations.

# How do you define CPU performance?

# **Defining Performance**

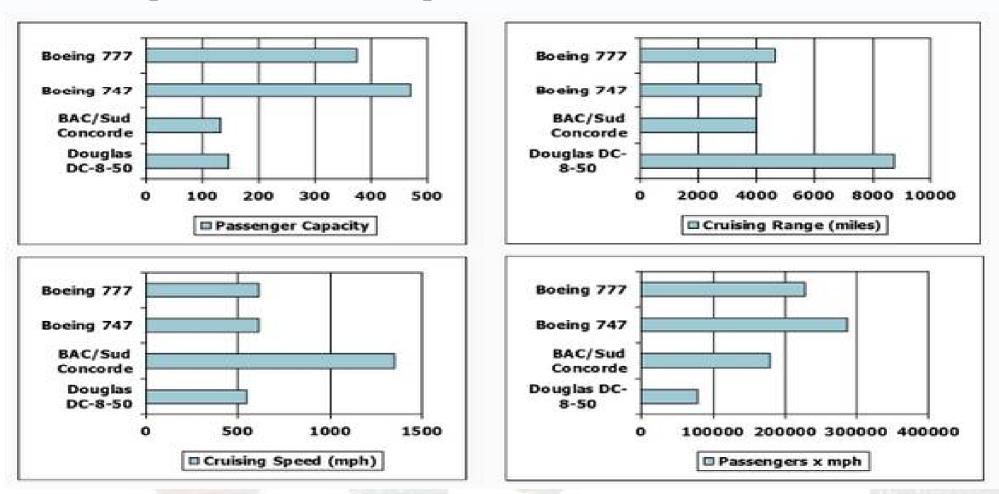

Which airplane has the best performance?

# **Defining Performance**

- Response time:

- How long it takes to do a task.

- It is also called execution time.

- It includes disk access, memory access, I/O activities.

- Throughput:

- Total amount of work done in a given time.

- e.g., tasks/transactions/... per hour.

- We'll focus on response time for now...

# **Relative Performance**

Performance defined as:

Then to evaluate two computers A & B .

Can be phrased as "Processor X is n times faster than Processor Y"

## **Relative Performance**

- Example: Assume a program runs in

- 10s on Processor A.

- 15s on Processor B.

- How much is A faster than B.

$$\frac{Execution\,Time\,of\,B}{Execution\,Time\,of\,A}\!=\!\frac{15}{10}\!=\!1.5$$

So, A is 1.5 times faster than B

# **Execution Time**

- How do you measure execution time?

- Elapsed time

- Total response time, including all aspects

- Processing, I/O, OS overhead, idle time

- Determines system performance

- CPU time

- Time spent processing a given job

- Discounts I/O time, other jobs' shares

- Different programs are affected differently by CPU and system performance

# **CPU Clocking**

Operation of digital hardware governed by a constant-rate clock

- Clock frequency (rate): cycles per second

- e.g., 4.0GHz = 4000MHz =  $4.0 \times 10^9$ Hz

- Clock period: duration of a clock cycle

- e.g.,  $250ps = 0.25ns = 250 \times 10^{-12}s$

### **CPU Time**

CPUTime = CPUClock Cycles × Clock Cycle Time

= CPUClock Cycles

Clock Rate

- Performance improved by

- Reducing number of clock cycles

- Increasing clock rate

- Hardware designer must often trade off clock rate against cycle count

### **CPU Time**

Computer A run a program in 10 seconds with a 2 GHz clock. We have to design a computer B such that it can run the same program within 6 seconds. Determine the clock rate for computer B. Assume that due to increase in clock cycle rate, CPU design of computer B is affected, and it requires 1.2 times as many clock cycles as computer A for execution this program.

## **CPU Time Example**

- Computer A: 2GHz clock, 10s CPU time

- Designing Computer B such that:

- Aim for 6s CPU time

- Can do faster clock, but causes 1.2 × clock cycles

- How fast must Computer B clock be?

$$Clock Rate_{B} = \frac{Clock Cycles_{B}}{CPU Time_{B}} = \frac{1.2 \times Clock Cycles_{A}}{6s}$$

$$Clock Cycles_A = CPU Time_A \times Clock Rate_A$$

$$=10s \times 2GHz = 20 \times 10^9$$

Clock Rate<sub>B</sub> =

$$\frac{1.2 \times 20 \times 10^9}{6s} = \frac{24 \times 10^9}{6s} = 4$$

GHz

## **Instruction Performance**

- The computer had to execute the instructions to run the program.

- The execution time must depend on the number of instructions in a program.

## **Instruction Count and CPI**

Clock Cycles =Instruction Count  $\times$ Cycles per Instruction

CPU Time =Instruction Count  $\times$ CPI  $\times$ Clock Cycle Time  $= \frac{Instruction Count \times CPI}{Clock Rate}$

- Instruction Count for a program

- Determined by program, ISA and compiler

- Average cycles per instruction

- Determined by CPU hardware

# **CPI Example**

- Computer A Cycle Time = 250ps, CPI = 2.0

- Computer B Cycle Time = 500ps, CPI = 1.2

- Same ISA

- Which is faster? By how much?

# **CPI Example**

- Computer A: Cycle Time = 250ps, CPI = 2.0

- Computer B: Cycle Time = 500ps, CPI = 1.2

- Same ISA

- Which is faster, and by how much?

## **CPI in More Detail**

If different instruction classes take different numbers of cycles

Clock Cycles =

$$\sum_{i=1}^{n}$$

(CPI<sub>i</sub> ×Instruction Count<sub>i</sub>)

Weighted average CPI

$$CPI = \frac{Clock Cycles}{Instruction Count} = \sum_{i=1}^{n} \left( CPI_i \times \frac{Instruction Count_i}{Instruction Count} \right)$$

Relative frequency

# **CPI Example**

#### **Comparing Code Segments**

A compiler designer is trying to decide between two code sequences for a computer. The hardware designers have supplied the following facts:

|     | CPI for each instruction class |   |   |

|-----|--------------------------------|---|---|

|     | A                              | В | С |

| CPI | 1                              | 2 | 3 |

For a particular high-level language statement, the compiler writer is considering two code sequences that require the following instruction counts:

|               | Instruction counts for each instruction class |   |   |

|---------------|-----------------------------------------------|---|---|

| Code sequence | A                                             | В | C |

| 1             | 2                                             | 1 | 2 |

| 2             | 4                                             | 1 | 1 |

Which code sequence executes the most instructions? Which will be faster? What is the CPI for each sequence?

# **CPI Example**

Alternative compiled code sequences using instructions in classes

A, B, C

| Class            | А | В | С |

|------------------|---|---|---|

| CPI for class    | 1 | 2 | 3 |

| IC in sequence 1 | 2 | 1 | 2 |

| IC in sequence 2 | 4 | 1 | 1 |

- Sequence 1: IC = 5

- Clock Cycles= 2×1 + 1×2 + 2×3= 10

- Avg. CPI = 10/5 = 2.0

- Sequence 2: IC = 6

- Clock Cycles= 4×1 + 1×2 + 1×3= 9

- Avg. CPI = 9/6 = 1.5

# **Performance Summary**

### **The BIG Picture**

$$\begin{array}{c} \text{CPUTime} = & \frac{\text{Instructions}}{\text{Program}} \times & \frac{\text{Clock cycles}}{\text{Instruction}} \times & \frac{\text{Seconds}}{\text{Clock cycle}} \end{array} \\ \end{array}$$

- Performance depends on

- Algorithm: affects IC, possibly CPI

- Programming language: affects IC, CPI

- Compiler: affects IC, CPI

- Instruction set architecture: affects IC, CPI

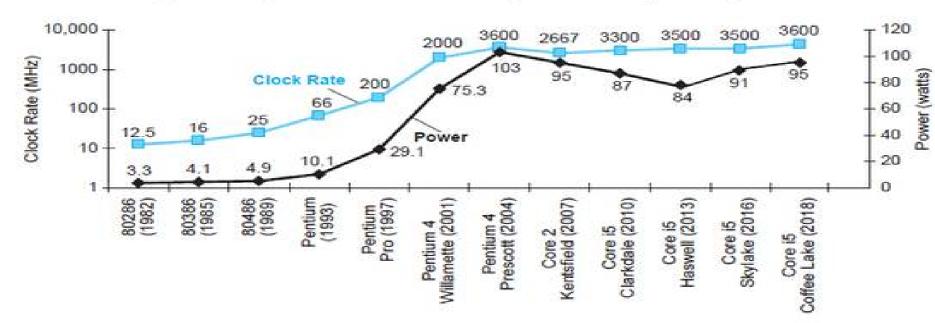

## **Power Trends**

In CMOS IC technology

Power = Capacitive load × Voltage<sup>2</sup> × Frequency

# **Topics**

- 1. Basic Processor Architecture

- 2. Different Types of Processor Architectures

- 3. RISC-V Processor Architecture

- 4. RISC-V Instruction Set Architecture

- 5. Programming RISC-V using assembly language

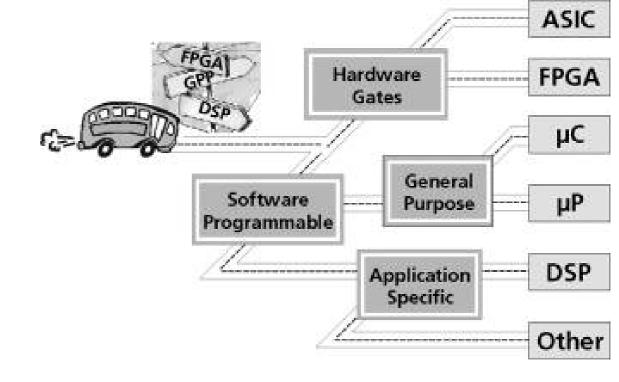

## Processors Types

- General Purpose Processor

- Digital Signal Processor

- Vector Processor

- Application specific Processor

## Flynn Taxonomy

The matrix below defines the 4 possible classifications according to Flynn

| SISD                              | SIMD                                |  |

|-----------------------------------|-------------------------------------|--|

| Single Instruction, Single Data   | Single Instruction, Multiple Data   |  |

| MISD                              | MIMD                                |  |

| Multiple Instruction, Single Data | Multiple Instruction, Multiple Data |  |

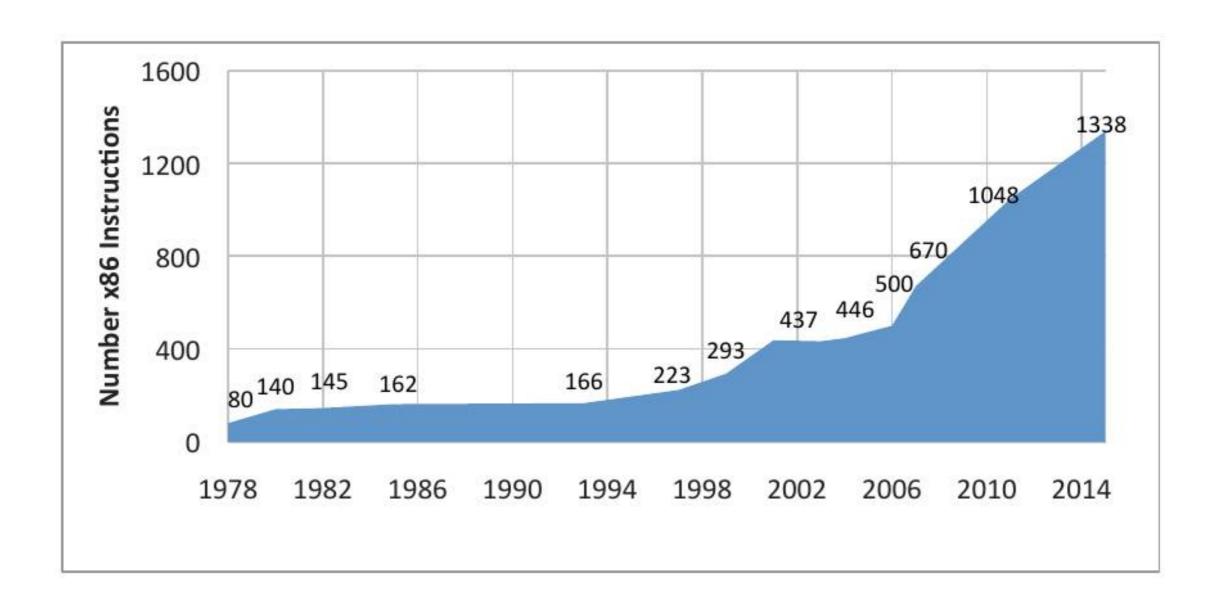

# **Types of Processor ISA**

Reduced Instruction Set Computing (RISC) vs Complex Instruction Set Computing (CISC)

| Aspect                 | RISC                                         | CISC                      |

|------------------------|----------------------------------------------|---------------------------|

| Instructions Per Cycle | Small and fixed length                       | Large and variable length |

| Instruction Complexity | Simple and standardised                      | Complex and versatile     |

| Instruction Execution  | Single clock cycle                           | Several clock cycles      |

| RAM Usage              | Heavy use of RAM                             | More efficient use of RAM |

| Memory                 | Increased memory usage to store instructions | Memory efficient coding   |

| Cost                   | Cheaper than CISC                            | Higher                    |

### RISC vs CISC

The RISC approach has several advantages over CISC:

- Simplifies Hardware Implementation: It simplifies the hardware implementation of the processor, as fewer instructions need to be decoded and executed. This can lead to faster execution times and lower power consumption.

- Higher Instruction Level Parallelism: RISC processors typically have a higher instruction-level parallelism, allowing them to execute multiple instructions simultaneously, which can further improve performance.

- **Simplicity:** The simplicity of the RISC instruction set makes it easier to develop compilers and other software tools that can generate efficient code for the processor.

### RISC vs CISC

RISC is a processor design philosophy that emphasizes simplicity and efficiency by using a small set of simple and general-purpose instructions.

- The *complex instruction set computing* (CISC), employs a larger set of more complex instructions that can perform multiple operations in a single instruction.

- RISC architectures prioritize simplicity and execute one instruction per clock cycle, resulting in streamlined designs and efficient decoding.

- CISC architectures, on the other hand, employ complex instructions capable of performing multiple actions but may require several clock cycles for execution. Both the CPUs aim to enhance CPU performance.

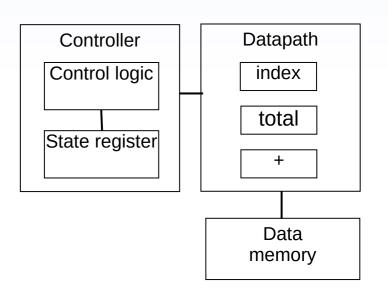

# Single-purpose processors

Digital circuit designed to execute exactly one program a.k.a. coprocessor, accelerator or peripheral

**Features**

Contains only the components needed to execute a single program

No program memory

**Benefits**

**Fast**

Low power

Small size

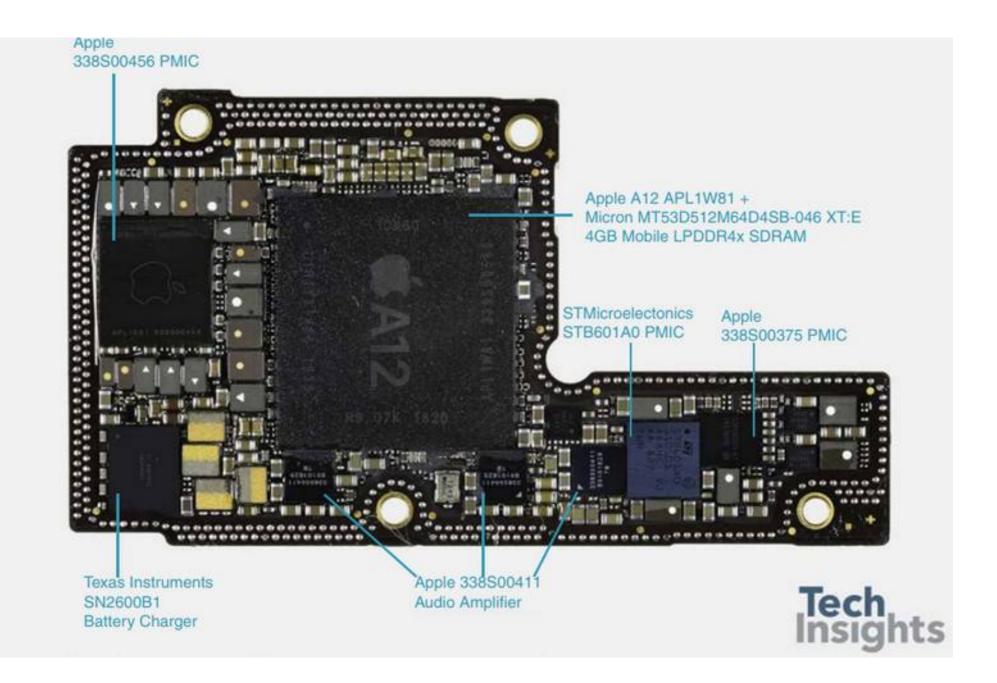

## Embedded System Processor Architecture

- Reduced Instruction Set Computing (RISC):

- Common architectures: ARM, RISC-V.

- 3 Simple, efficient instruction set optimized for low power and high performance.

- System on Chip (SoC):

- Frequently used in embedded systems.

- Integrates CPU, memory, peripherals, and other components on a single chip.

- Microcontroller Units (MCUs):

- 3 Often used in simpler embedded applications.

- Includes integrated peripherals like ADCs, DACs, timers, and communication interfaces

- Real-Time Capabilities:

- Designed for deterministic performance and real-time operating system (RTOS) support.

- Low Power Consumption:

- <sup>3</sup> Architectures and components optimized for minimal power usage.

- Integrated Analog and Digital Peripherals:

- Features like GPIOs, serial communication interfaces, and specialized hardware accelerators.

Datapath

Registers

Custom ALU

Data

memory

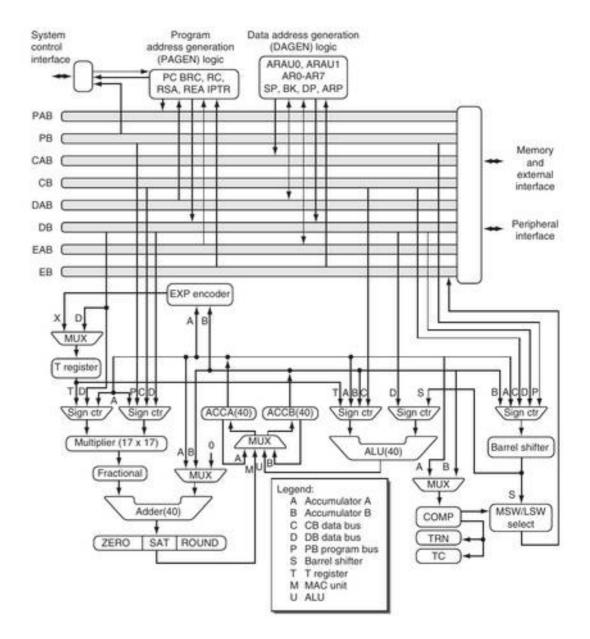

## Digital Signal Processor

### **Specialized Instruction Set:**

Optimized for mathematical operations like multiply-accumulate (MAC). Single-cycle multiply and MAC instructions.

#### **Harvard Architecture:**

Separate program and data memories to allow simultaneous access and increase throughput.

### **Specialized Data Path:**

Multiple data buses and address buses.

Dedicated hardware for specific tasks such as FFT (Fast Fourier Transform) and filters.

### **High-Performance ALUs:**

Multiple arithmetic logic units (ALUs) to perform parallel operations.

Support for fixed-point and floating-point arithmetic.

### **Circular and Bit-Reversed Addressing:**

Efficiently manage circular buffers and data structures used in signal processing.

### **Low-Latency Memory Access:**

On-chip RAM with very low access latency.

Multi-level cache hierarchy optimized for predictable access patterns.

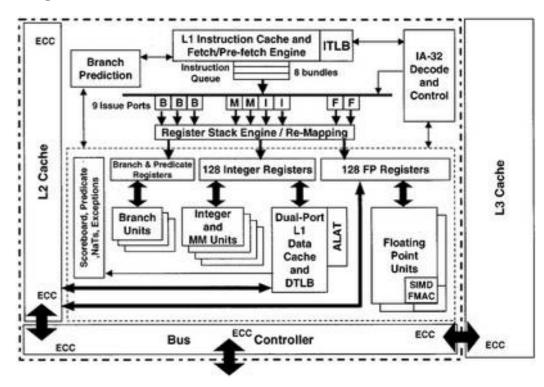

## General-Purpose Processor (GPP) Architecture

#### Complex Instruction Set Computing (CISC):

- Common architecture: x86.

- Rich instruction set with complex instructions.

- Often integrates many features directly in hardware.

#### Multi-Core and Hyper-Threading:

- Multiple cores for parallel processing.

- Hyper-threading for improved performance through parallel execution within each core.

#### Large Cache Hierarchy:

- Multiple levels of cache (L1, L2, L3) to reduce latency and increase speed.

- 3 Advanced Branch Prediction and Speculative Execution:

- Techniques to predict instruction paths and execute ahead to improve performance.

#### Integrated Memory Management Unit (MMU):

Manages virtual memory, enabling sophisticated operating system features.

#### High-Speed Interconnects:

Fast communication between CPU, memory, and peripherals.

#### Graphics Processing Unit (GPU) Integration:

3 Some GPPs include integrated GPUs for handling graphics processing tasks.

# Topics

- 1. Basic Processor Architecture

- 2. Different Types of Processor Architectures

- 3. RISC-V Processor Architecture

- 4. RISC-V Instruction Set Architecture

- 5. Programming RISC-V using assembly language

### **RISC-V Processor Architecture**

The RISC-V (pronounced as risk-five) architecture is an open-source instruction set architecture (ISA) implementation of reduced instruction set computing RISC.

RISC-V is open-hardware architecture, its open source allows anyone to utilize the ISA.

### **History of RISC-V**

- Prof. Krste Asanović and graduate students Yunsup Lee and Andrew Waterman started the RISC-V instruction set in May 2010 as part of the <u>Parallel Computing Laboratory</u> (Par Lab) at UC Berkeley, of which Prof. David Patterson was Director.

- No patents were filed related to RISC-V in any of these projects, as the RISC-V ISA itself does not represent any new technology.

• RISC processor implementations—including some based on other open ISA standards— are widely available from various vendors worldwide.

## Processor Architecture

### **Base Instruction Set**

RV32I Base Integer Instruction Set, 32-bit

RV32E Base Integer Instruction Set (embedded), 32-bit

RV64I Base Integer Instruction Set, 64-bit

### **Extension:**

| Name     | Description                                                |  |  |  |

|----------|------------------------------------------------------------|--|--|--|

| M        | Standard Extension for Integer Multiplication and Division |  |  |  |

| A        | Standard Extension for Atomic Instructions                 |  |  |  |

| F        | Standard Extension for Single-Precision Floating-Point     |  |  |  |

| D        | Standard Extension for Double-Precision Floating-Point     |  |  |  |

| Zicsr    | Control and Status Register (CSR) Instructions             |  |  |  |

| Zifencei | Instruction-Fetch Fence                                    |  |  |  |

| G        | Shorthand for the IMAFDZicsr_Zifencei base and extension:  |  |  |  |

| С        | Standard Extension for Compressed Instructions             |  |  |  |

### **Base and Extension of RISC-V**

- Four base integer ISAs

- RV32E, RV32I, RV64I, RV128I

- RV32E is 16-register subset of RV32I

- Only <50 hardware instructions needed for base

- Standard extensions

- M: Integer multiply/divide

- A: Atomic memory operations (AMOs + LR/SC)

- F: Single-precision floating-point

- D: Double-precision floating-point

- G = IMAFD, "General-purpose" ISA

- Q: Quad-precision floating-point

- All the above are a fairly standard RISC encoding in a fixed 32-bit instruction format

- Above user-level ISA components frozen in 2014

- Supported forever after

# RISCV: Registers and Mapping

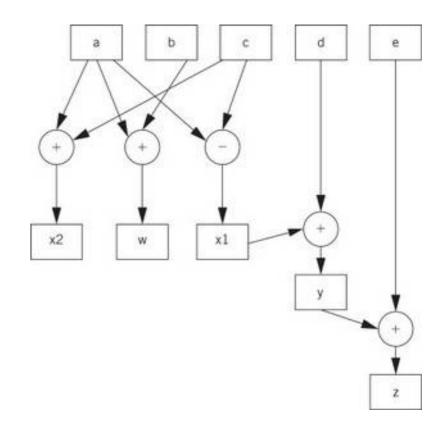

RISC-V uses a memory-mapped I/O architecture, which means that input and output operations, memory access, and peripheral access are all performed using the same load and store instructions.

- This unified approach simplifies the instruction set and enhances the flexibility and efficiency of the architecture. There are two basic types of instructions:

- Instructions that either load memory into registers or store data from registers into memory

- Instructions that perform arithmetical or logical operations between two registers

# Why RISC-V

**Open Hardware:** Allowing anyone to design, implement, and customize processors without restrictions, fostering innovation and collaboration within the community.

**Royalty-Free:** There are no licensing fees, reducing costs for developers and manufacturers.

**Security:** Rigorous security analysis and the implementation of custom security features, enhancing trustworthiness.

| ISA    | Pages | Words     | Hours to read | Weeks to read |

|--------|-------|-----------|---------------|---------------|

| RISC-V | 236   | 76,702    | 6             | 0.2           |

| ARM-32 | 2736  | 895,032   | 79            | 1.9           |

| x86-32 | 2198  | 2,186,259 | 182           | 4.5           |

|                                                      | ARM-32 (1986)                                          | Mistakes of the Past<br>MIPS-32 (1986)                                                     |                                                                                                                                  | Lessons learned<br>RV32I (2011)                                                                                                                                                                                                                                  |

|------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cost                                                 | Integer multiply<br>mandatory                          | Integer multiply<br>and divide manda-<br>tory                                              | erations. Integer                                                                                                                | No 8-bit and 16-bit op-<br>erations. Integer multi-<br>ply and divide optional<br>(RV32M)                                                                                                                                                                        |

| Simplicity                                           | struction execution.<br>Complex data<br>address modes. | extended imme-<br>diates. Some<br>arithmetic instruc-                                      | Complex procedure<br>call/return instruc-<br>tions (enter/leave),<br>Stack instructions<br>(push/pop), Com-<br>plex data address | Register x0 dedicated to<br>0. Immediates only sign-<br>extended. One data ad-<br>dressing mode. No con-<br>ditional execution. No<br>complex call/return or<br>stack instructions. No<br>traps for arithmetic over-<br>flow. Separate shift in-<br>structions   |

| Performance                                          | branches. Source                                       |                                                                                            | branches. At most                                                                                                                | Compare and branch in-<br>structions (no condition<br>codes). 3 registers per in-<br>struction. No load mul-<br>tiple. Source and desti-<br>nation registers fixed in<br>instruction format. Con-<br>stant immediates. PC not<br>a general purpose regis-<br>ter |

|                                                      | line length when<br>writing the PC as                  | Delayed branch.<br>Delayed load. HI<br>and LO registers<br>just for multiply<br>and divide | eral purpose (AX,<br>CX, DX, DI, SI                                                                                              | No delayed branch. No<br>delayed load. General<br>purpose registers                                                                                                                                                                                              |

| Room for growth                                      | Limited available opcode space                         | Limited available<br>opcode space                                                          |                                                                                                                                  | Generous available op-<br>code space                                                                                                                                                                                                                             |

| Program size                                         |                                                        | Only 32-bit instruc-<br>tions (+microMIPS<br>as separate ISA)                              |                                                                                                                                  | 32-bit instructions + 16-<br>bit RV32C extension                                                                                                                                                                                                                 |

| Ease of pro-<br>gramming /<br>compiling /<br>linking | memory. Irregu-                                        | memory. Inconsis-                                                                          | PC-relative data ad-                                                                                                             | data addressing. Sym-                                                                                                                                                                                                                                            |

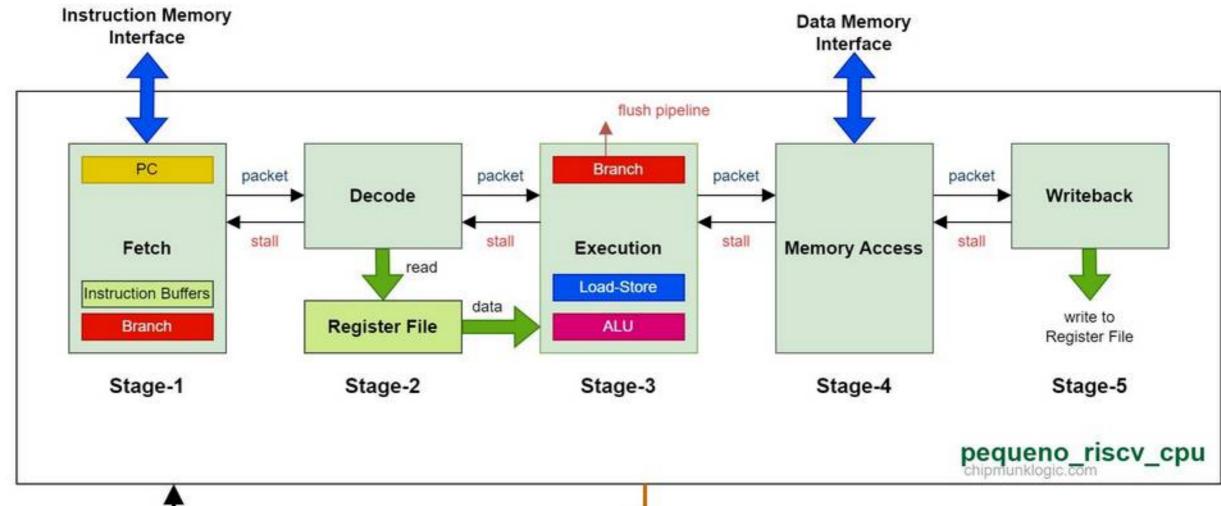

## Types of RISC-V Processor Architectures

- RISC-V provides a detailed, open Instruction Set Architecture (ISA), which serves as a blueprint for designing processors architecture.

- Single-Cycle Architecture:

- Multi-Cycle Architecture:

- Pipelined Architecture:

- Superscalar Architecture:

- Out-of-Order Execution:

- Very Long Instruction Word (VLIW) Architecture:

- Vector Processing Architecture:

- Custom Instruction Set Extensions:

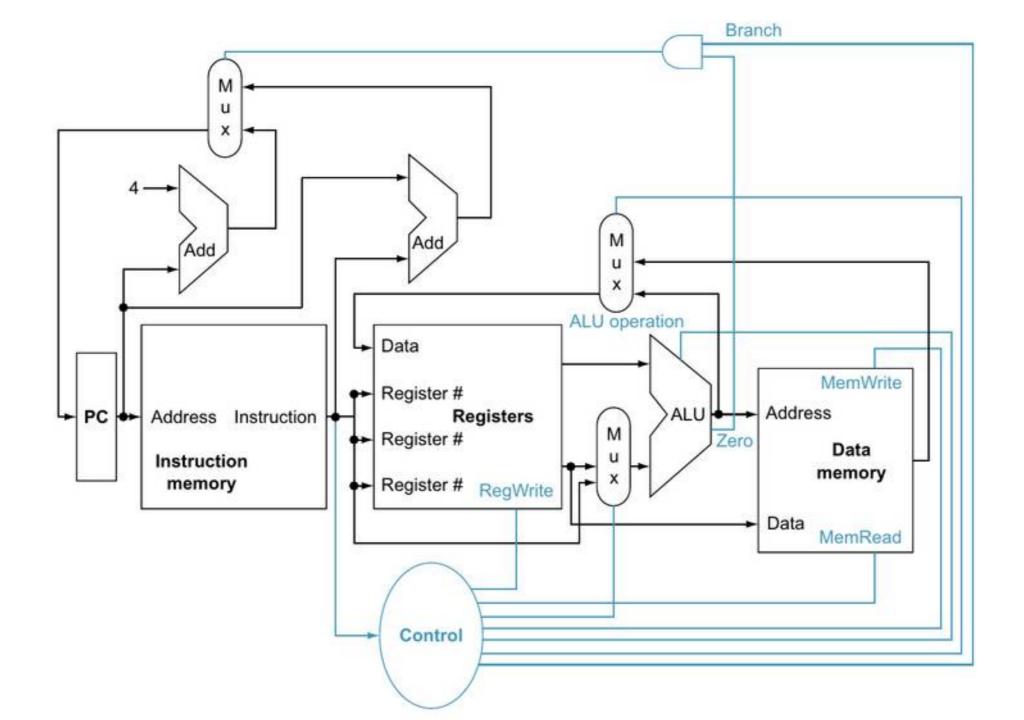

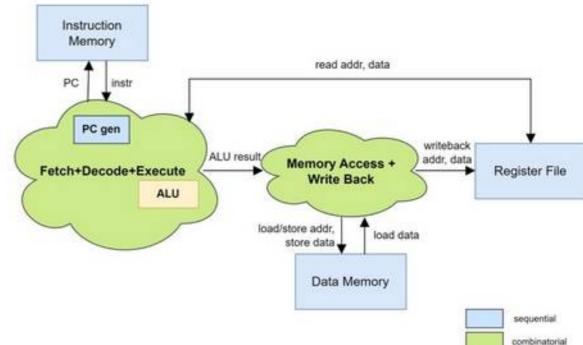

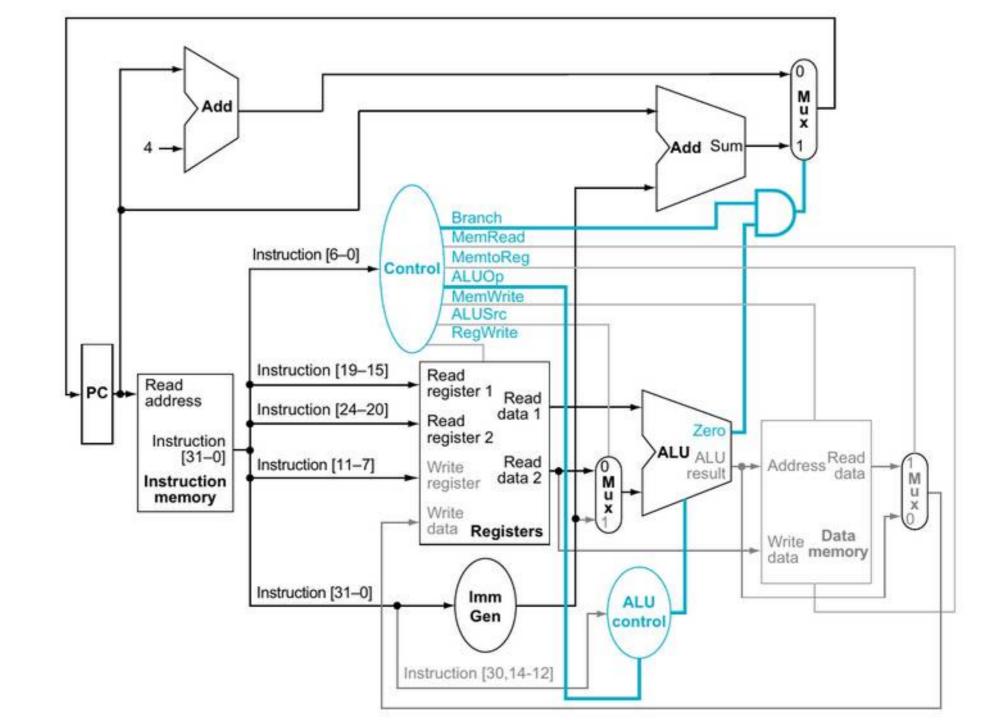

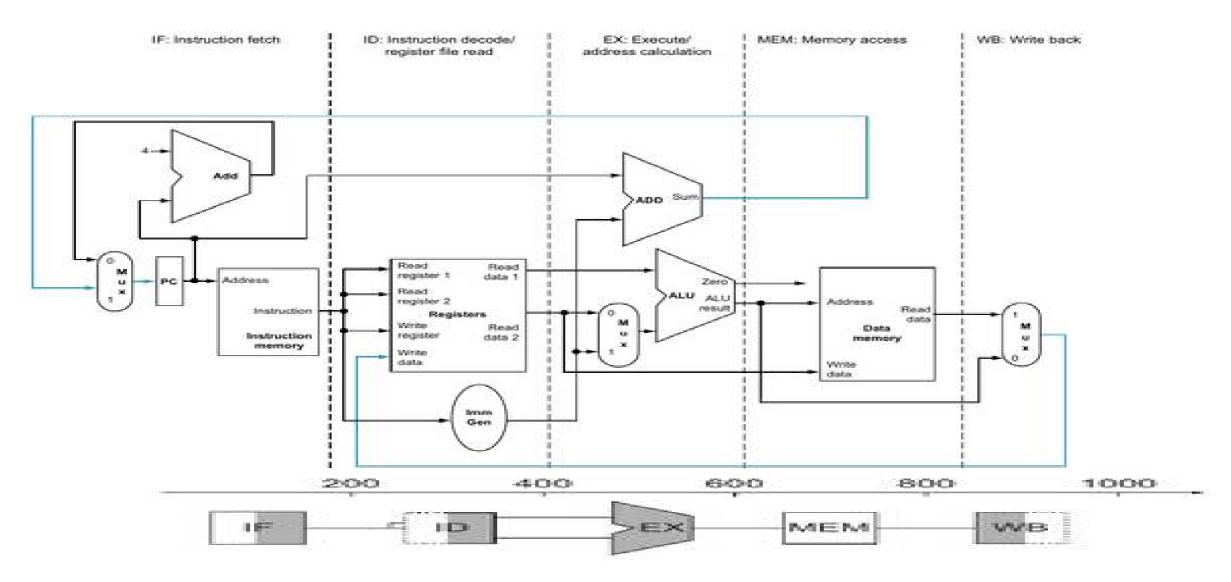

## Defining/Designing RISC-V Processor Architecture

- Fetch: Retrieve the instruction from memory.

- Decode: Interpret the instruction and prepare operands.

- Execute: Perform the computation or operation (ALU operations, branches).

- Memory: Access memory for load/store operations.

- Writeback: Write the result to the register file or memory.

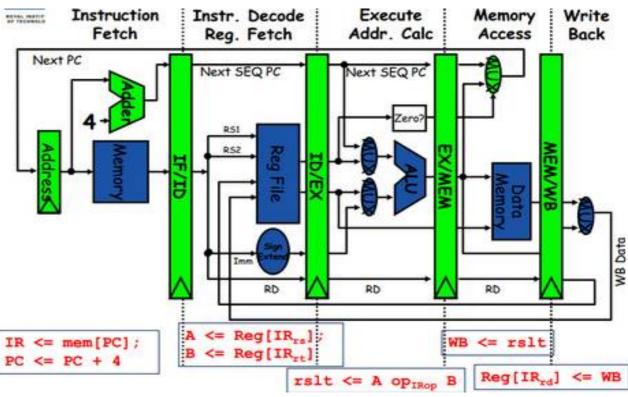

# 5 Stages of Processor Arch

### Fetch Unit

Function: Retrieves instructions from memory.

PC Usage: The PC holds the address of the next instruction to be fetched. After fetching an instruction, the PC is typically incremented to point to the next instruction address. Example: If the starting address of the first instruction is 0x8000000, the Fetch Unit will

fetch the instruction from address 0x8000000 initially.

### Decode Unit

Function: Interprets the fetched instruction to determine its operation and operands.

Memory Access: Decodes memory addresses and identifies whether they are for RAM, ROM, or I/O devices. It also decodes which registers are involved.

ALU: Determines the type of ALU operation required (e.g., addition, subtraction) and prepares operands for execution.

Example: Decodes an instruction to add two registers and prepare the operands for the ALU.

### **Execute Unit**

Function: Performs the arithmetic or logical operations as specified by the instruction.

ALU: Executes ALU operations (e.g., addition, subtraction) using the operands provided by the Decode Unit.

Memory Access: Computes effective addresses for load/store operations.

Example: Executes an addition operation on two registers or calculates the address for a load instruction.

### **Memory Unit**

Function: Accesses memory or I/O based on the address computed in the Execute stage.

Memory Access: Performs read/write operations to RAM or memory-mapped I/O devices based on the effective address.

Example: Reads data from address 0x00002000 in RAM or writes data to a memory-mapped I/O device at 0x20000000.

### **Write Back Unit**

Function: Writes the result of computations or memory accesses back to the register file or memory.

Memory Access: Updates the register file with results from the Memory Unit or ALU operations.

Example: Writes the result of an addition operation back to a register or stores data retrieved from memory to a register.

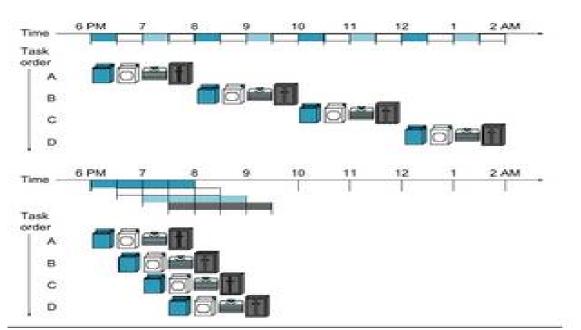

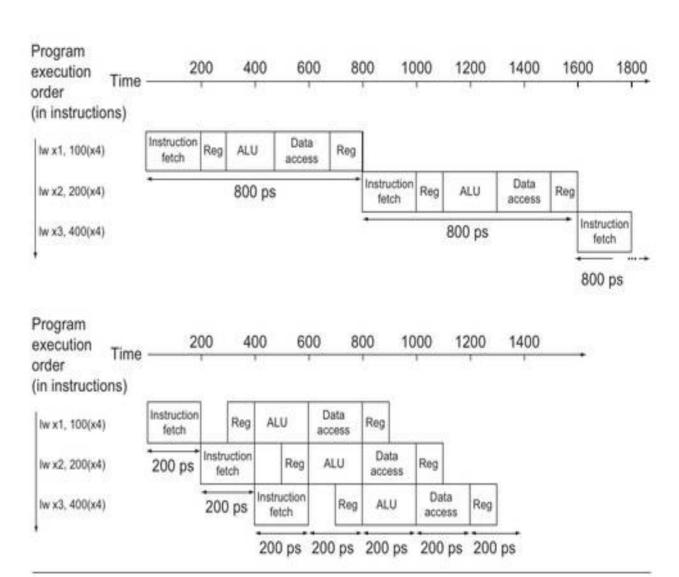

#### **Pipe-lined VS Single Cycle Processor Architecture**

- 1. Fetch instruction from memory.

- Read registers and decode the instruction.

- 3. Execute the operation or calculate an address.

- 4. Access an operand in data memory (if necessary).

- 5. Write the result into a register (if necessary).

### **5 Stage Pipelined Processor Architecture**

### Topics

- 1. Basic Processor Architecture

- 2. Different Types of Processor Architectures

- 3. RISC-V Processor Architecture

- 4. RISC-V Instruction Set Architecture

- 5. Programming RISC-V using assembly language

# Instruction Set Architecture is like the language that a computer's hardware understands. I

- ISA is a set of instructions that tells the computer's processor what to do. These instructions are basic operations like adding two numbers, moving data from one place to another, or jumping to a different part of a program.

- The ISA defines the "rules" of computer architecture or the "language" that the CPU uses to execute instructions.

- It determines what the processor can do. If a processor supports a particular ISA, it can execute any program written in that ISA.

- It also ensures that different programs can run on different computers as long as those computers understand the same ISA.

- It's like setting the vocabulary and grammar for a conversation between software and hardware.

- It is is the language that a computer's hardware understands. I

### Commercial ISA

- Commercial ISAs are proprietary.

- Commercial ISAs are only popular in certain market domains.

- Commercial ISAs come and go.

- Popular commercial ISAs are complex.

- Commercial ISAs alone are not enough to bring up applications.

- Popular commercial ISAs were not designed for extensibility.

- A modified commercial ISA is a new ISA.

### OpenRISC

- OpenRISC has condition codes and branch delay slots, which complicate higher performance implementations.

- OpenRISC uses a fixed 32-bit encoding and 16-bit immediates, which precludes a denser instruction encoding and limits space for later expansion of the ISA.

- OpenRISC does not support the 2008 revision to the IEEE 754 floating-point standard.

- The OpenRISC 64-bit design had not been completed when we began.

#### **RISCV Instructions Set**

RISC-V (Reduced Instruction Set Computing V) is an open standard instruction set architecture (ISA) that is designed to be scalable and extensible. The number of instructions in RISC-V can vary based on the specific subset or extensions of the ISA being used. Here's a breakdown of the primary RISC-V instruction sets and their respective instruction counts:

#### Base ISA:

- RV32I (32-bit Integer): The base integer instruction set for 32-bit processors includes approximately 47 instructions.

- RV64I (64-bit Integer): The base integer instruction set for 64-bit processors extends RV32I and includes a few additional instructions specific to 64 bit operations.

### Instruction Extensions

#### Standard Extensions:

- > M (Multiply/Divide): Adds multiply and divide instructions.

- > A (Atomic): Adds atomic instructions for synchronization.

- F (Single-Precision Floating-Point): Adds single-precision floating-point instructions.

- > D (Double-Precision Floating-Point): Adds double-precision floating-point instructions.

- Q (Quad-Precision Floating-Point): Adds quad-precision floating-point instructions.

- > C (Compressed): Adds compressed instructions to reduce code size.

#### Other Extensions:

- > B (Bit-Manipulation): Adds instructions for bit manipulation.

- > V (Vector): Adds vector processing instructions.

- ► P (Packed-SIMD): Adds packed SIMD instructions.

- > Z (Various small extensions): These include specific sets of instructions like Zifencei for instruction-fence or Zicsr for control and status registers.

### **Basic RISCV Processor**

#### • The 47 standard instructions in RV32I include:

- > Arithmetic Instructions: ADD, SUB, MUL, etc.

- Logical Instructions: AND, OR, XOR, etc.

- > Immediate Instructions: ADDI, ORI, XORI, etc.

- Load Instructions: LB, LH, LW, etc.

- Store Instructions: SB, SH, SW, etc.

- Branch Instructions: BEQ, BNE, BLT, etc.

- > Jumps: JAL, JALR

- System Instructions: ECALL, EBREAK

- Other Instructions: NOP, AUIPC, LUI, etc.

| 31         | 25 24     | 20        | 19     | 15 14 | 12  | 11 7        |         | 0         |

|------------|-----------|-----------|--------|-------|-----|-------------|---------|-----------|

|            |           | imm[31:12 |        |       |     | rd          | 0110111 | U lui     |

| 5          |           | imm[31:12 |        |       |     | rd          | 0010111 | U auipe   |

|            | imm[2     | 0 10:1 11 | 19:12] |       | - 1 | rd          | 1101111 | J jal     |

|            | m[11:0]   |           | rsl    | 00    |     | rd          | 1100111 | 1 jalr    |

| imm[12]10  |           | rs2       | rsl    | 00    |     | imm[4:1]11] | 1100011 | B beq     |

| imm[12]10  |           | rs2       | rs1    | - 00  |     | imm[4:1]11] | 1100011 | B bne     |

| imm[12]10  | :5]       | rs2       | rs1    | 10    | 0   | imm[4:1[11] | 1100011 | B blt     |

| imm[12]10  |           | rs2       | rsl    | 10    |     | imm[4:1 11] | 1100011 | B bge     |

| imm[12]10  |           | rs2       | rs1    | 11    |     | imm[4:1]11] | 1100011 | B bltu    |

| imm[12]10: |           | rs2       | rsl    | - 11  |     | imm[4:1 11] | 1100011 | B bgcu    |

|            | m[11:0]   |           | rsl    | .00   |     | rd          | 0000011 | I lb      |

|            | m[11:0]   |           | rsl    | - 00  |     | rd          | 0000011 | I lh      |

|            | m[11:0]   | 13        | rs1    | 01    |     | rd          | 0000011 | I lw      |

|            | m[11:0]   |           | rsl    | 10    |     | rd          | 0000011 | I lbu     |

|            | m[11:0]   | armen ill | rsl    | 10    |     | rd          | 0000011 | 1 lhu     |

| imm[11:5   |           | rs2       | rs1    | .00   |     | imm[4:0]    | 0100011 | S sb      |

| imm[11:5   |           | rs2       | rsl    | - 00  |     | imm[4:0]    | 0100011 | S sh      |

| imm[11:5   |           | rs2       | rs1    | 01    |     | imm[4:0]    | 0100011 | S sw      |

|            | m[11:0]   |           | rsl    | - 00  |     | rd          | 0010011 | I addi    |

| im         | m[11:0]   | 11        | rsl    | 01    |     | rd          | 0010011 | I slti    |

|            | m[11:0]   |           | rs1    | 01    |     | rd          | 0010011 | I sltiu   |

|            | m[11:0]   |           | rs1    | 10    |     | rd          | 0010011 | I xori    |

|            | m[11:0]   |           | rsl    | 11    |     | rd          | 0010011 | I ori     |

|            | m[11:0]   | ne 13     | rsl    | 11    |     | rd          | 0010011 | I andi    |

| 0000000    |           | shamt     | rsl    | 00    |     | rd          | 0010011 | I slli    |

| 0000000    |           | shamt     | rsl    | 10    |     | rd          | 0010011 | I srli    |

| .0100000   |           | shamt     | rs1    | 10    |     | rd          | 0010011 | I srai    |

| 0000000    |           | rs2       | rsl    | - 00  |     | rd          | 0110011 | R add     |

| 0100000    |           | rs2       | rs1    | 00    |     | rd          | 0110011 | R sub     |

| 0000000    |           | rs2       | rs1    | .00   |     | rd          | 0110011 | R sll     |

| 0000000    |           | rs2       | rsl    | 01    |     | rd          | 0110011 | R slt     |

| 0000000    |           | rs2       | rsl    | - 01  |     | rd          | 0110011 | R sltu    |

| 0000000    |           | rs2       | rs1    | 10    |     | rd          | 0110011 | R xor     |

| 0000000    |           | rs2       | rsl    | 10    |     | rd          | 0110011 | R srl     |

| 0100000    |           | rs2       | rsl    | 10    |     | rd          | 0110011 | R sra     |

| 0000000    |           | rs2       | rs1    | 11    |     | rd          | 0110011 | R or      |

| 0000000    | 6         | rs2       | rsl    | - 11  |     | rd          | 0110011 | R and     |

| .0000      | pred      | succ      | 00000  | .00   |     | 00000       | 0001111 | I fence   |

| 0000       | 0000      | . 0000    | 00000  | - 00  | 1   | 00000       | 0001111 | I fence.i |

| 0000       | 000000000 | 0         | 00000  | - 00  | 0   | 00000       | 1110011 | I ecall   |

| 0000       | 00000000  | 1         | 00000  | .00   | 0   | 00000       | 1110011 | I ebreak  |

|            | csr       |           | rs1    | .00   | 1   | rd          | 1110011 | 1 csrrw   |

|            | CSF       |           | rsl    | 01    | 0   | rd          | 1110011 | I csrrs   |

|            | est       |           | rsl    | 01    | 1   | rd          | 1110011 | I estre   |

|            | csr       |           | zimm   | 10    | 1   | rd          | 1110011 | I csrrwi  |

|            | CSF       |           | zimm   | 110   | 0   | rd          | 1110011 | I csrrsi  |

|            | CST       |           | zimm   | 11    | 1   | rd          | 1110011 | I estrei  |

### Types of RISCV ISA

#### **RISC-V Instruction Set:**

The RISC-V instruction set is a collection of instructions that define the operations a RISC-V processor can perform.

These instructions are designed to be simple, efficient, and easily extensible, allowing for a high degree of customization and optimization.

#### **Instruction Types:**

- 1. R-Type (Register Type): Used for register-register arithmetic and logical operations.

- 2. I- Type (Instruction Type): Used for immediate arithmetic, load instructions, and register-immediate operations.

- 3. S-Type (Store Type): Used for store instructions.

- 4. U-Type (Upper Immediate Type): Used for upper immediate instructions

- 5. B-Type (Branch Type): Used for conditional branch instructions.

- 6. J-Type (Jump Type): Used for jump instructions like JAL.

- 7. F-Type (Floating-Point) Instructions

- 8. A-Type (Atomic) Instructions

- 9. C-Type (Compressed) Instructions

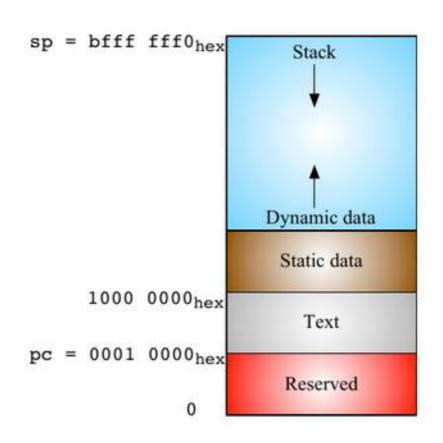

## Registers

- Total Registers: 32 general-purpose registers, additional special-purpose and control registers.

- General Purpose Registers: x0 to x31, with specific roles for some registers.

- Special Purpose Registers: Includes PC, SP, GP, TP.

- Program Counter (PC): Holds the address of the current instruction being executed.

- Instruction Register (IR): Holds the current instruction being executed (in some implementations).

- Stack Pointer (SP): Points to the top of the stack.

- Global Pointer (GP): Points to the global data region.

- Thread Pointer (TP): Points to the thread-local storage.

- Control and Status Registers: Includes MSR, MEPC, MCAUSE, MSTATUS, MTVEC.

- Machine Status Register (MSR): Controls machine-level status and configuration.

- Machine Exception Program Counter (MEPC): Holds the address of the instruction where an exception occurred.

- Machine Cause Register (MCAUSE): Contains information about the cause of the last exception.

- Machine Status Register (MSTATUS): Holds the status of the machine, including interrupts and mode.

- Machine Trap Vector Base Address Register (MTVEC): Base address for the trap vector.

- Floating-Point Registers: If included, f0 to f31 for floating-point operations.

| Register name | Symbolic name | Description                          | Saved by |

|---------------|---------------|--------------------------------------|----------|

|               |               | 32 integer registers                 |          |

| x0            | Zero          | Always zero                          |          |

| x1            | ra            | Return address                       | Caller   |

| x2            | sp            | Stack pointer                        | Callee   |

| х3            | gp            | Global pointer                       |          |

| x4            | tp            | Thread pointer                       |          |

| x5            | t0            | Temporary / alternate return address | Caller   |

| x67           | 11-2          | Temporary                            | Caller   |

| x8            | s0/fp         | Saved register / frame pointer       | Callee   |

| x9            | s1            | Saved register                       | Callee   |

| x10-11        | a0-1          | Function argument / return value     | Caller   |

| x12-17        | a2-7          | Function argument                    | Caller   |

| x18-27        | s2-11         | Saved register                       | Callee   |

| x28-31        | t36           | Temporary                            | Caller   |

### **RISC-V Instruction Format**

| 6      | 7                                    | 11                                                        | 12                                                                                                                   | 14                                                                                                                                                                                               | 15                                                                                                                                                                                                           | 19                                                                                           | 20                                                                                                                                                                                                                                                                        | 24                                                                                                                                                                                                                                                                                                          | 25                                                                                                                                                                                                                                                                                                                  | 26                                                                                                                                                                                                                                                                                                                                           | 27                                                                                                                                                                                                                                                                                                                                                                         |

|--------|--------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| opcode | rd                                   | 1                                                         | ct3                                                                                                                  | fun                                                                                                                                                                                              |                                                                                                                                                                                                              | rs1                                                                                          | 2                                                                                                                                                                                                                                                                         | rs                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                     | t7                                                                                                                                                                                                                                                                                                                                           | func                                                                                                                                                                                                                                                                                                                                                                       |

| opcode | rd                                   | 1                                                         | ct3                                                                                                                  | fun                                                                                                                                                                                              | 4                                                                                                                                                                                                            | rs1                                                                                          |                                                                                                                                                                                                                                                                           | ]                                                                                                                                                                                                                                                                                                           | 1:0                                                                                                                                                                                                                                                                                                                 | nm[1                                                                                                                                                                                                                                                                                                                                         | in                                                                                                                                                                                                                                                                                                                                                                         |

| opcode | n[4:0]                               | imm                                                       | ct3                                                                                                                  | fun                                                                                                                                                                                              |                                                                                                                                                                                                              | rs1                                                                                          | 2                                                                                                                                                                                                                                                                         | rs                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                     | 1:5]                                                                                                                                                                                                                                                                                                                                         | imm[1                                                                                                                                                                                                                                                                                                                                                                      |

| opcode | 4:1 11]                              | imm[                                                      | ct3                                                                                                                  | fun                                                                                                                                                                                              |                                                                                                                                                                                                              | rs1                                                                                          | 2                                                                                                                                                                                                                                                                         | rs                                                                                                                                                                                                                                                                                                          | 5]                                                                                                                                                                                                                                                                                                                  | 10:5                                                                                                                                                                                                                                                                                                                                         | nm[12                                                                                                                                                                                                                                                                                                                                                                      |

| opcode | rd                                   | 1                                                         |                                                                                                                      |                                                                                                                                                                                                  |                                                                                                                                                                                                              | :12]                                                                                         | m[31                                                                                                                                                                                                                                                                      | im                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                            |

| opcode | rd                                   | 1                                                         |                                                                                                                      |                                                                                                                                                                                                  | 2]                                                                                                                                                                                                           | 11 19:1:                                                                                     | 10:1                                                                                                                                                                                                                                                                      | 1[20]                                                                                                                                                                                                                                                                                                       | imm                                                                                                                                                                                                                                                                                                                 | j                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                            |

|        | opcode<br>opcode<br>opcode<br>opcode | rd opcode<br>n[4:0] opcode<br>4:1 11] opcode<br>rd opcode | rd         opcode           imm[4:0]         opcode           imm[4:1 11]         opcode           rd         opcode | ct3         rd         opcode           ct3         rd         opcode           ct3         imm[4:0]         opcode           ct3         imm[4:1 11]         opcode           rd         opcode | funct3         rd         opcode           funct3         rd         opcode           funct3         imm[4:0]         opcode           funct3         imm[4:1 11]         opcode           rd         opcode | funct3 rd opcode funct3 rd opcode funct3 imm[4:0] opcode funct3 imm[4:1 11] opcode rd opcode | rs1         funct3         rd         opcode           rs1         funct3         rd         opcode           rs1         funct3         imm[4:0]         opcode           rs1         funct3         imm[4:1 11]         opcode           :12]         rd         opcode | 2         rs1         funct3         rd         opcode           rs1         funct3         rd         opcode           2         rs1         funct3         imm[4:0]         opcode           2         rs1         funct3         imm[4:1 11]         opcode           m[31:12]         rd         opcode | rs2         rs1         funct3         rd         opcode           rs1         funct3         rd         opcode           rs2         rs1         funct3         imm[4:0]         opcode           rs2         rs1         funct3         imm[4:1 11]         opcode           imm[31:12]         rd         opcode | rs2         rs1         funct3         rd         opcode           11:0]         rs1         funct3         rd         opcode           rs2         rs1         funct3         imm[4:0]         opcode           s]         rs2         rs1         funct3         imm[4:1 11]         opcode           imm[31:12]         rd         opcode | t7         rs2         rs1         funct3         rd         opcode           nm[11:0]         rs1         funct3         rd         opcode           1:5]         rs2         rs1         funct3         imm[4:0]         opcode           10:5]         rs2         rs1         funct3         imm[4:1 11]         opcode           imm[31:12]         rd         opcode |

#### RISC-V Instructions and Formats

#### **RV32I Base Integer Instructions**